Fast and low‐power leading‐one detectors for energy‐efficient logarithmic computing - Ansari - 2021 - IET Computers & Digital Techniques - Wiley Online Library

How leading one prediction works: (a) Leading one detection and (b)... | Download Scientific Diagram

Leading one detectors and leading one position detectors - An evolutionary design methodology | Semantic Scholar

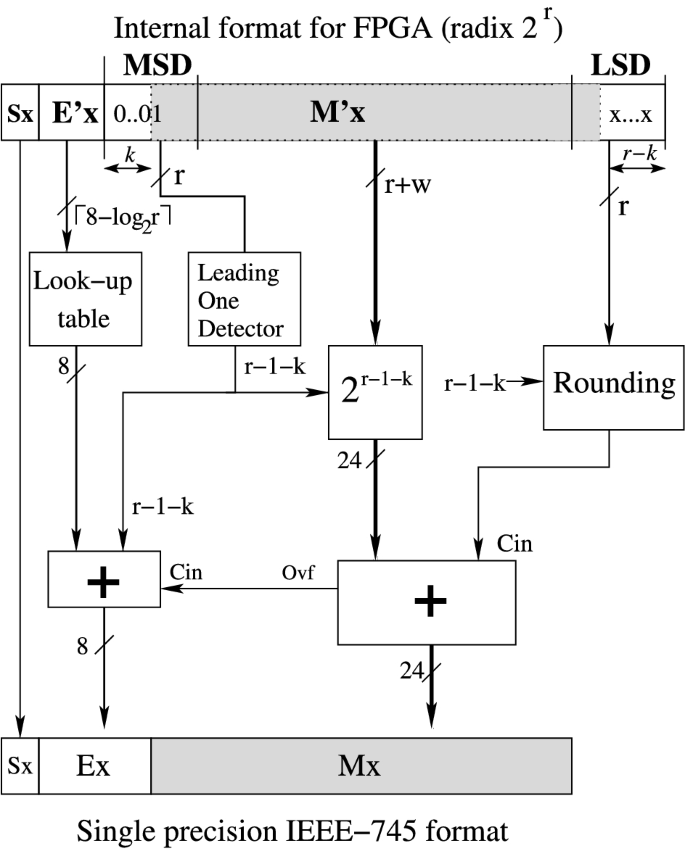

![PDF] Approximate Leading One Detector Design for a Hardware-Efficient Mitchell Multiplier | Semantic Scholar PDF] Approximate Leading One Detector Design for a Hardware-Efficient Mitchell Multiplier | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/fa224ea6de90f2c0107ced3535fabb2d2fa5eb18/3-Figure3-1.png)

PDF] Approximate Leading One Detector Design for a Hardware-Efficient Mitchell Multiplier | Semantic Scholar

![PDF] Approximate Leading One Detector Design for a Hardware-Efficient Mitchell Multiplier | Semantic Scholar PDF] Approximate Leading One Detector Design for a Hardware-Efficient Mitchell Multiplier | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/fa224ea6de90f2c0107ced3535fabb2d2fa5eb18/2-Figure2-1.png)

PDF] Approximate Leading One Detector Design for a Hardware-Efficient Mitchell Multiplier | Semantic Scholar

Leading one detectors and leading one position detectors - An evolutionary design methodology | Semantic Scholar

![A 4‐bit leading‐one detector [14] | Download Scientific Diagram A 4‐bit leading‐one detector [14] | Download Scientific Diagram](https://www.researchgate.net/publication/350299160/figure/fig1/AS:1151978897965073@1651664580127/A-4-bit-leading-one-detector-14_Q320.jpg)